# SHARP SERVICE MANUAL

CODE: 00ZAR5132TM1E

# **DIGITAL COPIER NO.2**

# MODEL AR-5132

|   |      | CONTENTS                          |  |

|---|------|-----------------------------------|--|

|   | [1]  | PRINCIPLES OF THE DIGITAL COPIER  |  |

|   | [2]  | PROCESS SECTION 2-1               |  |

|   | [3]  | DEVELOPING SECTION                |  |

|   | [4]  | PAPER FEED SECTION                |  |

|   | [5]  | TRANSPORT AND FUSING SECTION      |  |

|   | [6]  | HIGH VOLTAGE SECTION              |  |

|   | [7]  | RADF MECHANISM SECTION            |  |

|   | [8]  | DESK UNIT MECHANISM SECTION       |  |

|   | [9]  | ELECTRICAL SECTION                |  |

|   | [10] | RADF ELECTRICAL SECTION 10-1      |  |

|   | [11] | DESK UNIT ELECTRICAL SECTION 11-1 |  |

| l |      |                                   |  |

Parts marked with "<u>A</u>" is important for maintaining the safety of the set. Be sure to replace these parts with specified ones for maintaining the safety and performance of the set.

## CAUTION

This copier machine is a class 1 laser product that complies with 21CFR 1040.10 and 1040.11 of the CDRH standard and IEC825. This means that this machine does not produce hazardous laser radiation. The use of controls, adjustments or performance of procedures other than those specified herein may result in hazardous radiation exposure.

This laser radiation is not a danger to the skin, but when an exact focusing of the laser beam is achieved on the eye's retina, there is the danger of spot damage to the retina.

The following cautions must be observed to avoid exposure of the laser beam to your eyes at the time of servicing.

- 1) When a problem in the laser optical unit has occurred, the whole optical unit must be exchanged as a unit, not as individual parts.

- 2) Do not look into the machine with the main switch turned on after removing the developer unit, toner cartridge, and drum cartridge.

- 3) Do not look into the laser beam exposure slit of the laser optical unit with the connector connected when removing and installing the optical system.

- 4) The safety interlock switch is equipped.

Do not defeat the safety interlock by inserting wedges or other items into the switch slot.

LASER WAVE – LENGTH :  $785 \pm 15$ nm Pulse times : Out put power : 0.3mW ~ 0.6mW

#### CAUTION

INVISIBLE LASER RADIATION, WHEN OPEN AND INTERLOCKS DEFEATED. AVOID EXPOSURE TO BEAM.

#### VORSICHT

UNSICHTBARE LASERSTRAHLUNG, WENN ABDECKUNG GEÖFFNET UND SICHERHEITSVERRIEGELUNG ÜBERBRÜCKT. NICHT DEM STRAHL AUSSETZEN.

#### VARO !

AVATTAESSA JA SUOJALUKITUS OHITETTAESSA OLET ALTTIINA NÄKYMÄTTÖMÄLLE LASERSÄTEILYLLE ÄLÄ KATSO SÄTEESEEN.

#### ADVARSEL

USYNLIG LASERSTRÅLNING VED ÅBNING, NÅR SIKKERHEDSBRYDERE ER UDE AF FUNKTION. UNDGÅ UDSAETTELSE FOR STRÅLNING.

#### VARNING !

OSYNLIG LASERSTRÅLNING NÄR DENNA DEL ÄR ÖPPNAD OCH SPÄRREN ÄR URKOPPLAD. BETRAKTA EJ STRÅLEN. – STRÅLEN ÄR FARLIG.

# CONTENTS

| [1] | PRINCIPLES OF THE DIGITAL                                                                                                                                                                    | -1                   |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|     | <ol> <li>Difference in structure from analog copiers</li> <li>Basic composition of the digital copier</li> <li>Scanner section</li> <li>Laser unit</li> <li>Image process section</li> </ol> | -1<br>-1<br>-2<br>-2 |

| [2] | PROCESS SECTION         2           1. Outline         2           2. Basic process and composition         2                                                                                | -1                   |

| [3] | DEVELOPING SECTION31. Basic outline32. Basic composition33. Basic operation3                                                                                                                 | -1<br>-1             |

| [4] | PAPER FEED SECTION         4           1. Basic outline         4           2. Basic composition         4           3. Basic operation         4                                            | -1<br>-1             |

| [5] | TRANSPORT AND FUSING<br>SECTIONS51. Outline52. Basic composition and functions5                                                                                                              | -1                   |

| [6] | HIGH VOLTAGE SECTION       5         1. Outline       5         2. Basic composition       5                                                                                                 | -1                   |

|     |                                                                                                                                                                                              |                      |

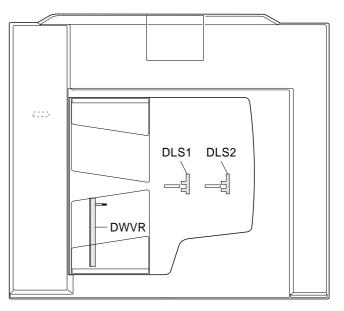

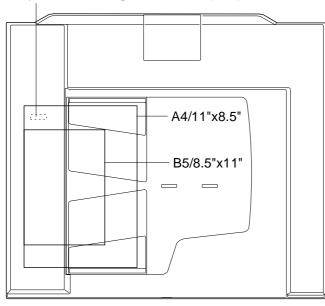

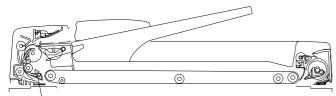

| [7]  | <b>RADF MECHANISM SECTIONS</b> 7-11. Operation flowchart7-12. Document size detection7-4                                                                                                                                                           |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [8]  | DESK UNIT MECHANISM<br>SECTION                                                                                                                                                                                                                     |

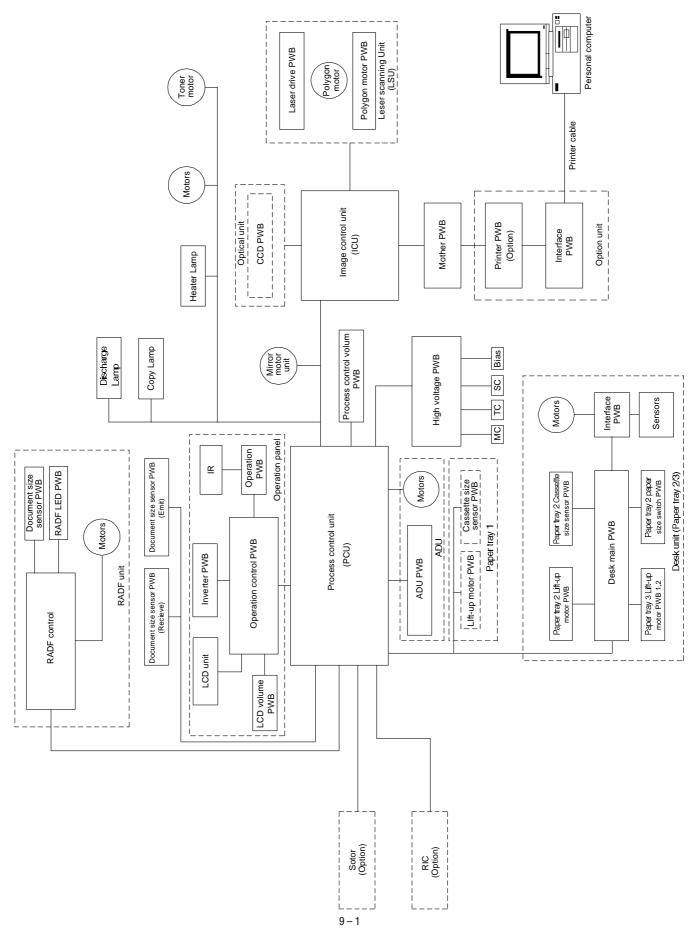

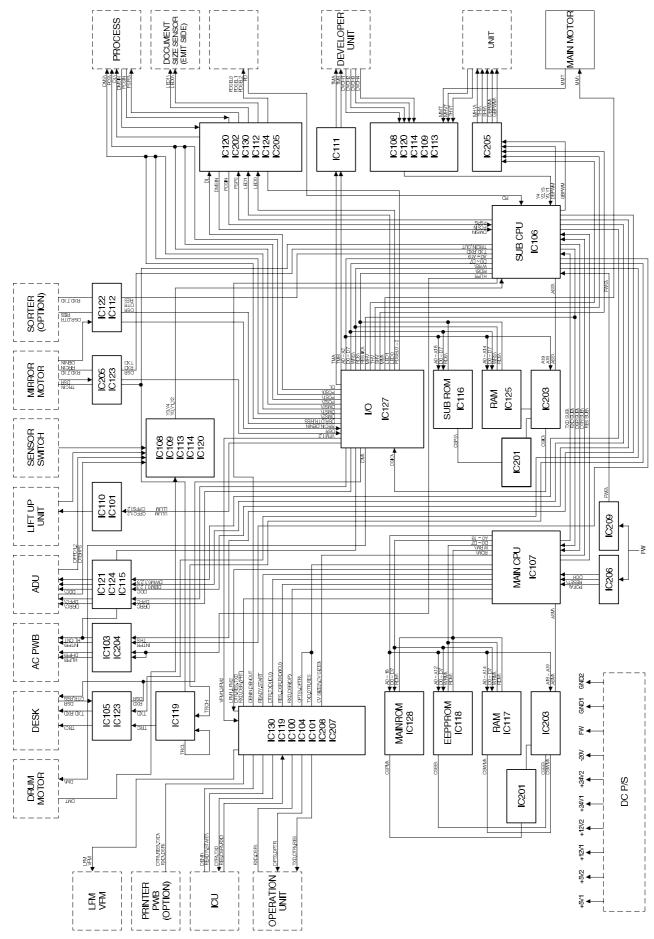

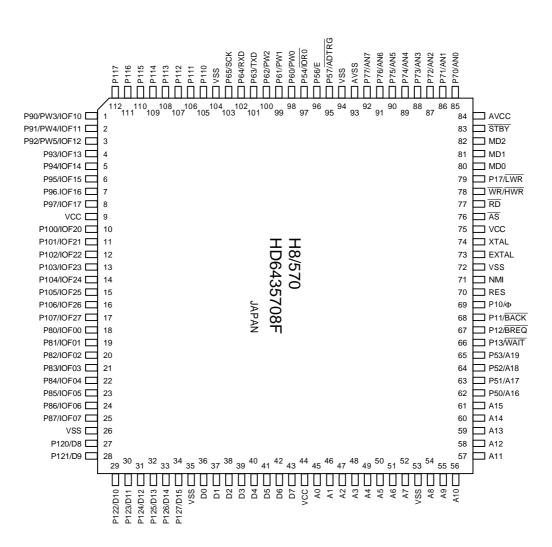

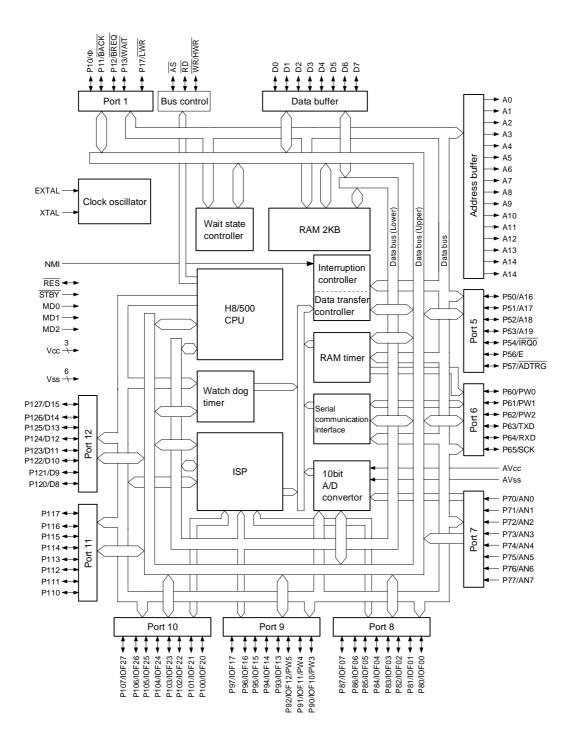

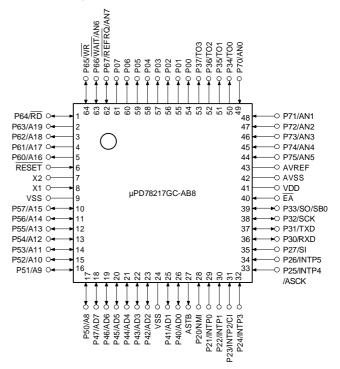

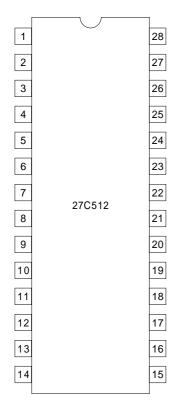

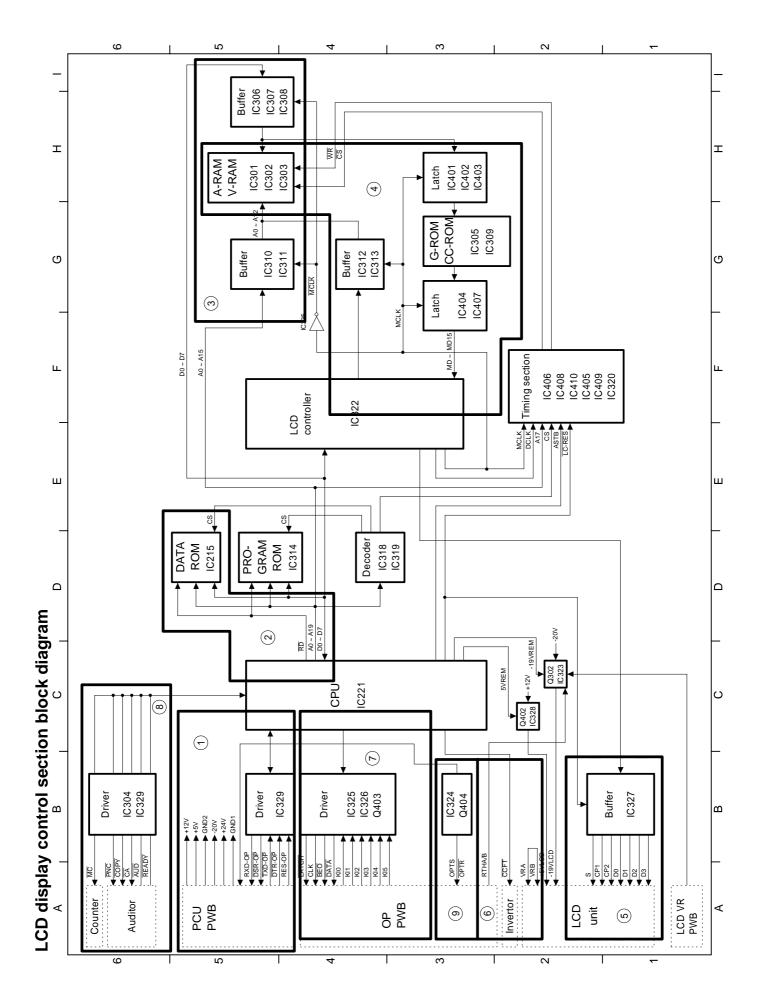

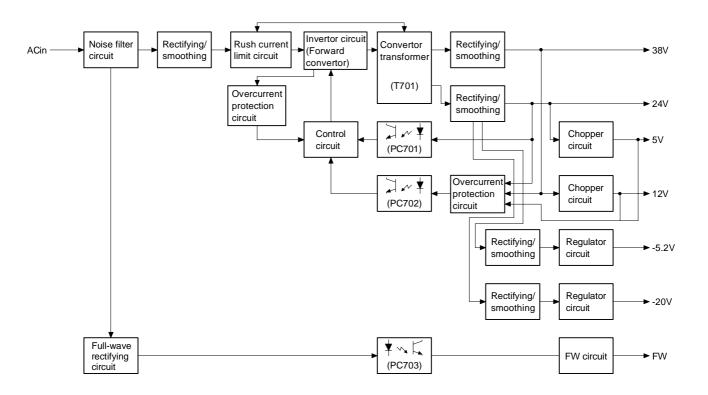

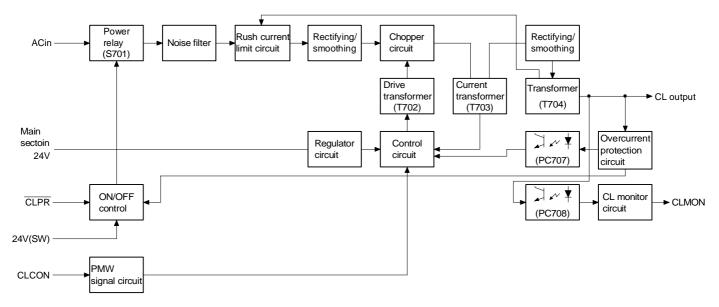

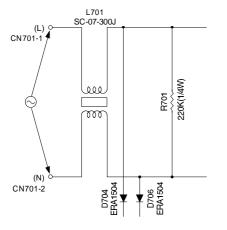

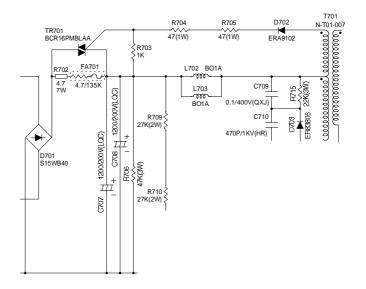

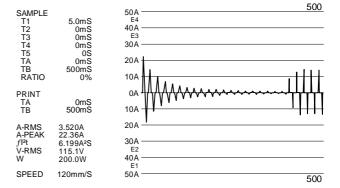

| [9]  | ELECTRICAL SECTION       9-1         1. Block diagram       9-1         2. ICU PWB       9-2         3. PCU PWB       9-6         4. Operation section       9-16         5. LCD display section       9-17         6. DC power circuit       9-22 |

| [10] | RADF ELECTRICAL SECTION       10-1         1. General       10-1         2. Block diagram       10-1         3. Operations       10-2                                                                                                              |

| [11] | DESK UNIT ELECTRICALSECTION11-11. Outline11-12. Block diagram11-13. Operational descriptions11-2                                                                                                                                                   |

# [1] PRINCIPLES OF THE DIGITAL COPIER

# 1. Difference in structure from analog copiers

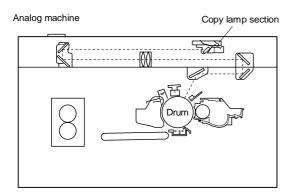

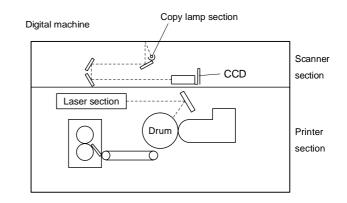

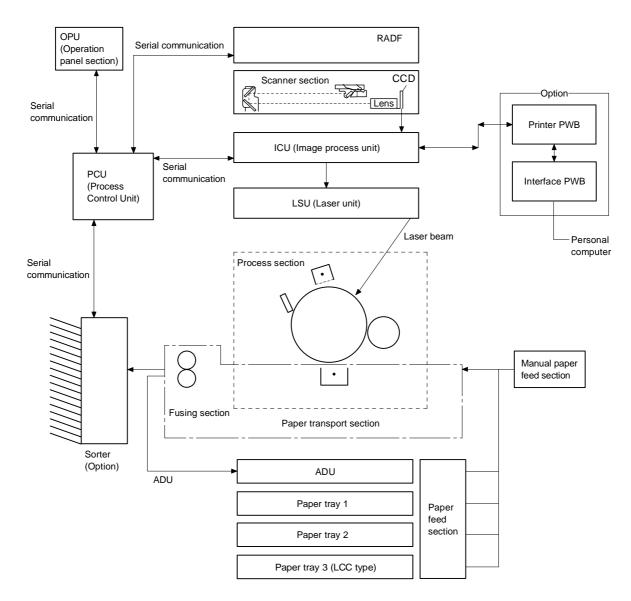

The digital copier is composed of the scanner section and the printer section. (Refer to the figures.)

In the digital copier, the reflected light is not directly radiated onto the OPC drum as in the analog copiers.

# 2. Basic composition of the digital copier

# (1) Basic operations of copying

- Image data are scanned in the scanner section and sent to the image process (ICU) PWB.

- ② The data are converted into printable data in the circuit of the image process (ICU) PWB.

- ③ The data are printed in the printer section.

# 3. Scanner section

### (1) How to scan an document

The scanner is provided with sensors which are arranged on one line. These sensors scan a horizontal line of an document at a time and the data are outputted sequentially. After completion of the line, the next line is scanned. The operation is repeated until one page is completed. The figure below shows that the images scanned by the sensors are sent to the ICU PWB sequentially.

The direction of the lines is called the "main scanning direction" and the direction of scanning the "sub scanning direction."

The above figure shows four elements in one line. Actually, however, there are thousands of elements in one line. The light receiving elements called CCD are used.

The resolution is an index value to express the capacity of scanners. The resolution shows how many light receiving elements are used in one inch (dpi, dot per inch).

While the sub scanning direction is used to control the motor which drives the optical system and to adjust the resolution to take in the images.

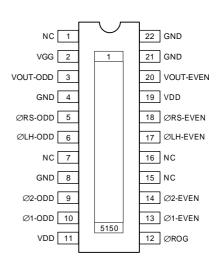

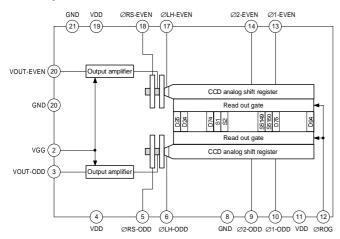

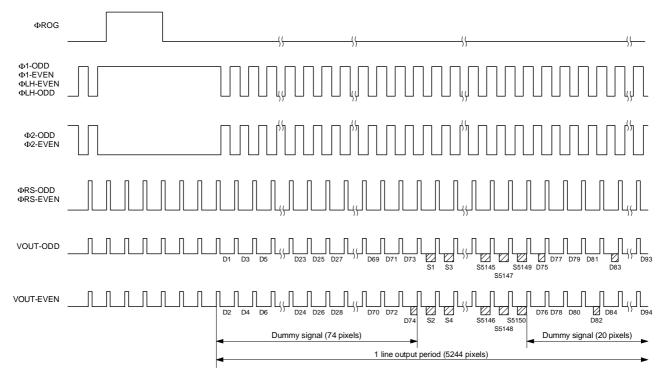

## (2) Basic structure of the scanner section

The scanner unit is the scanning section of the digital optical system. The light from the halogen lamp (which is driven by the DC power to suppress ripples) is reflected by the document and passed through three mirrors and the reduction lens to form images on the CCD elements (image sensors). This system is called the reduction type image sensor system. The light image (photo energy) formed on the CCD elements are converted into electrical signals (analog signals) by the CCD elements (Photo conversion).The output signals (analog signals) are converted into digital signals (A/D conversion) to perform various image processes. The resolution at that time is 400dpi.

# 4. Laser unit

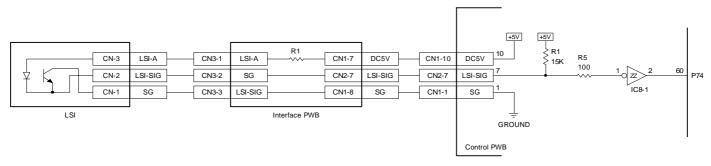

The image data sent from the ICU (image process PWB) are passed to the LSU (laser unit) and converted into laser beams.

# (1) Basic structure

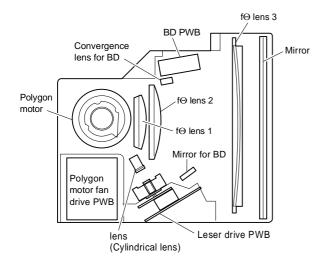

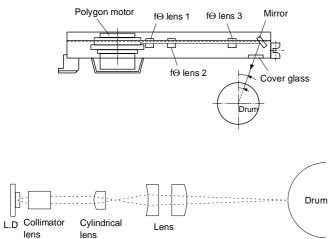

The LSU unit is the writing section of the digital optical system. The semiconductor laser is used as the light source. Images are formed by the polygon mirror and the  $f\theta$  lens on the OPC drum.

The internal structure is shown in the figure on the next page. The image data from the ICU are converted into DUTY signals for every gradations (256 steps), and the semiconductor laser on the laser emitting PWB is turned on/off according to the DUTY. The laser beams are passed through the collimator lens, the slit, the cylindrical lens, the polygon mirror, the f $\theta$  lens, and the mirror to form images in the shaft direction (main scanning direction) of the OPC drum. The laser emitting PWB is provided with the APC (Auto Power Control) to eliminate fluctuations in the laser power. The BD PWB serves to measure the writing point for the laser.

# (2) Composition

| Effective scanning width: | 302 mm                                            |  |

|---------------------------|---------------------------------------------------|--|

| Resolution:               | 400 dpi                                           |  |

| Beam diameter:            | main scanning 75 $\mu m,$ sub scanning 90 $\mu m$ |  |

| Image surface power:      | 0.3mW ~ 0.6mW                                     |  |

| Polygon motor:            | Brushless DC motor                                |  |

|                           | No. of mirrors $\rightarrow 6$                    |  |

### LSU internal structure

#### Side view

Sub scanning direction

### Functions of major parts

1 Collimator lens

Converges laser beams into parallel beams.

2 Cylindrical lens

Corrects laser beams in the sub scanning direction by shift of the surface of the polygon mirror.

③ BD (Mirror, lens, PWB)

Detects the start timing of the laser scanning.

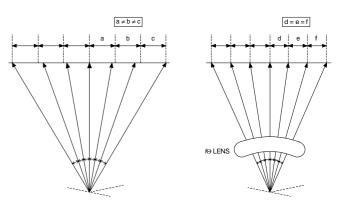

- (4) f $\theta$  lens

- Converges laser beams on a spot on the OPC drum.

- Equalizes the scanning speeds of laser beams at both ends and at the center.

- 5 Polygon mirror, polygon motor

- Reflects laser beams at constant rotation.

6 Semiconductor laser

Generates laser beams.

# 5. Image process section

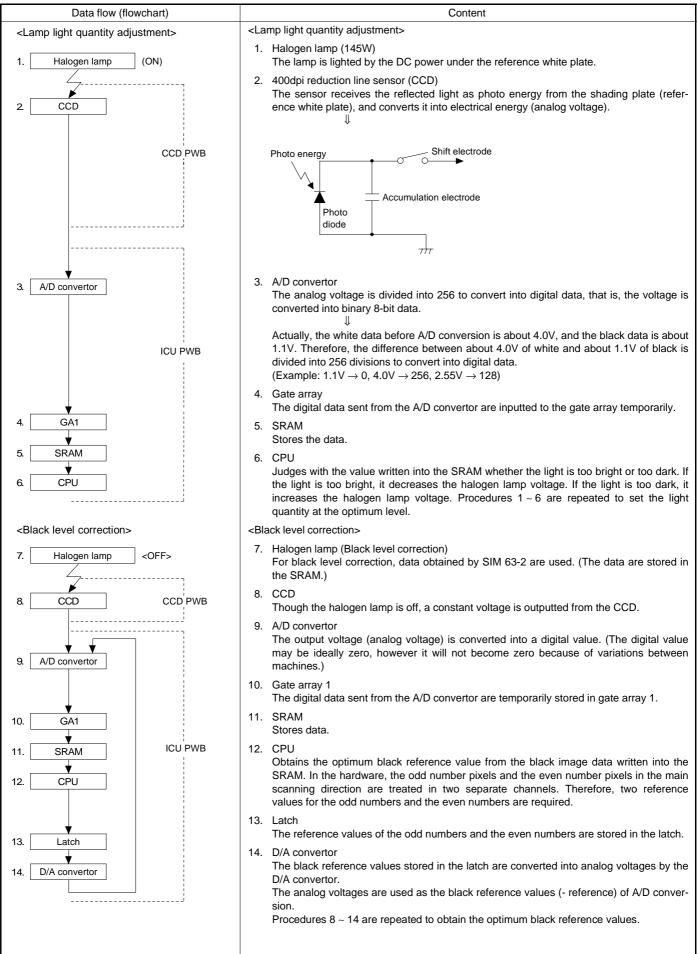

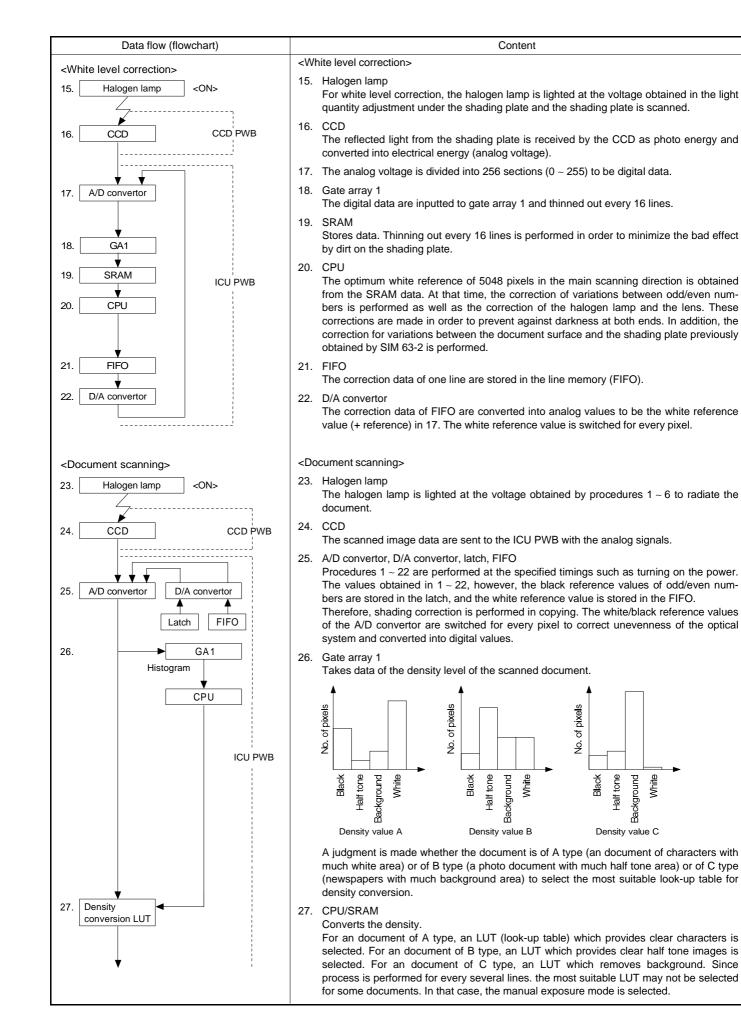

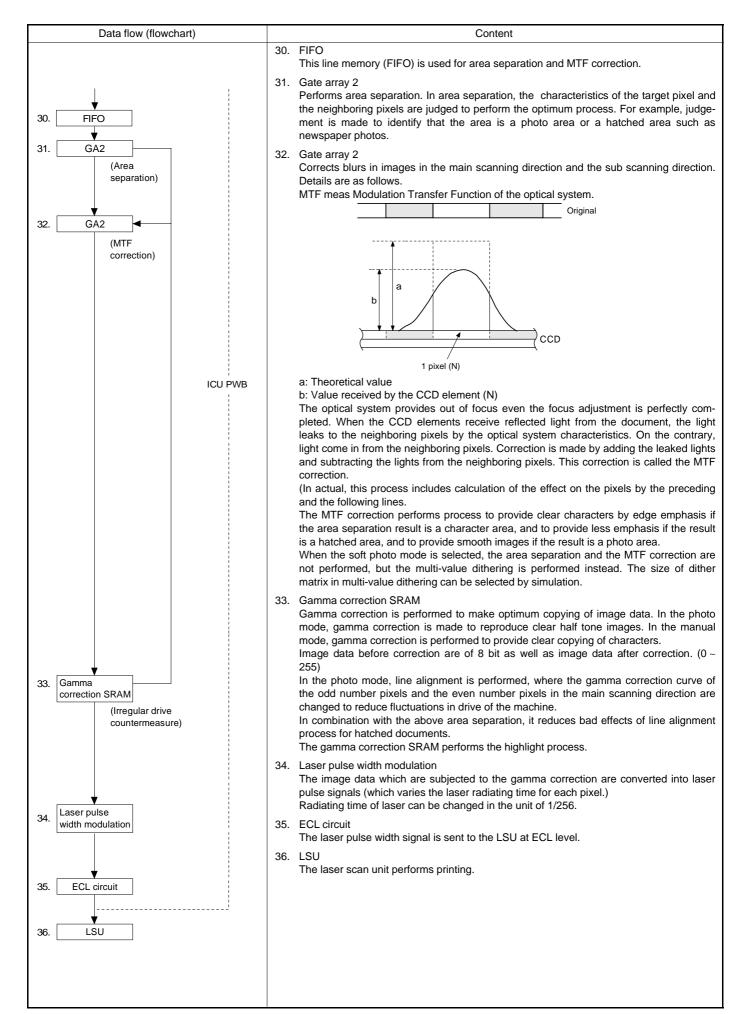

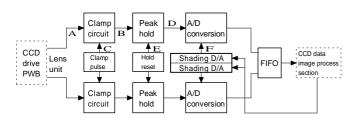

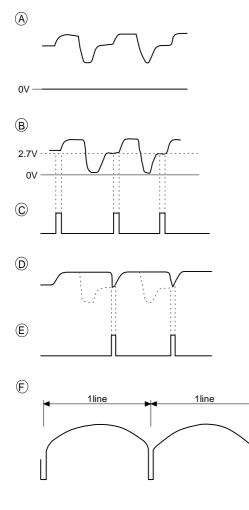

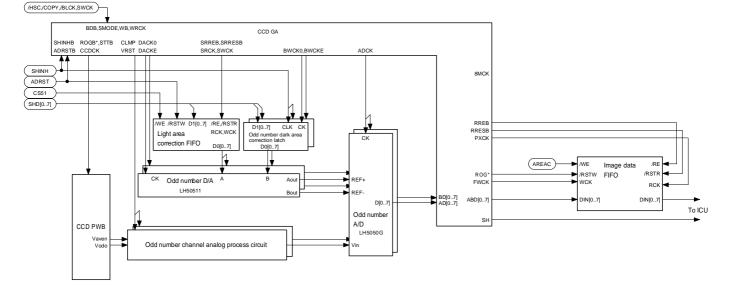

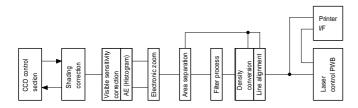

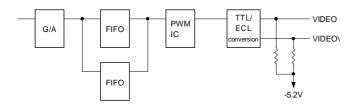

### (2) Image process section

The image process section is composed of gate arrays A and B, the CPU, and memories (SRAM, FIFO, EPROM). Gate array A forms data for shading correction and calculates histogram data for automatic exposure. Gate array B performs area separation, filter process, address generation for self printing, multi-value dithering, and electronic zooming of main scanning.

### ICU image process section block diagram

The CPU performs register setting and rewriting of LUT (look up table) every time when the user changes the mode. It also calculates the correction value of shading correction.

The figure below shows the flow of image signals.

### [Shading correction]

The analog image data from the CCD PWB are inputted to the CCD control section in the ICU and converted into digital data, and passed through gate array A in the ICU image process section, and written into the multi-function LUT (Look Up Table). (Path shown with dotted line in the above diagram.)

Gate array A performs thinning out of 16 lines at that time. Thinning out of 16 lines is performed when there is dirt on the shading plate.

### [Auto exposure]

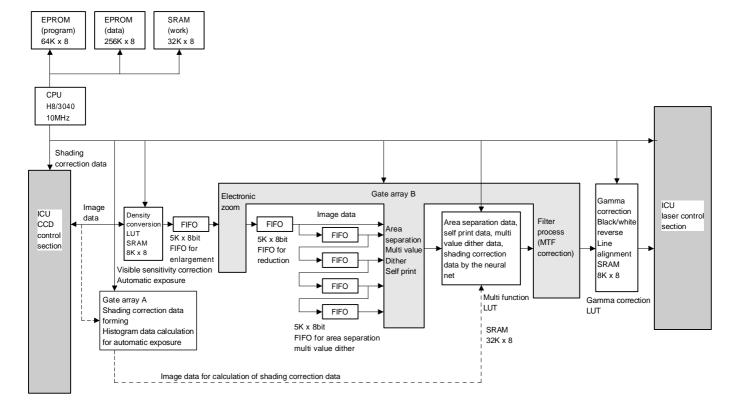

The analog image data from the CCD PWB are inputted to the CCD control section in the ICU and corrected by the shading data obtained from the above method and converted into digital data and inputted to gate array A. In gate array A, the total number data (simple histogram) of pixels in each density is calculated as shown in 1-5. The calculated data are used to judge that the document is of background type such as newspapers or of half tone type such as character documents. The data are calculated for each line. According to the data, the CPU selects the most suitable density conversion look up tables in the density conversion LUT.

### [Electronic zooming]

The image data, after auto exposure and the visual sensitivity correction, are written into the FIFO for enlargement. Gate array B controls the enable signal for reading the enlargement FIFO to thin out the read data, enlarging images. For example, in enlargement of 200%, the read enable signal is provided for every pixel to make enlargement. The image data thinned out for enlargement are inputted to gate array B and the primary interpolation is performed as shown in 1-6. (For details, refer to 1-6.) The image data thinned out primarily are written into the reduction FIFO. The enable signal for writing is controlled to thin out for reduction.

#### [Area separation]

After electronic zooming, the image data are written into the FIFO for area separation/filter/multi-value dithering. There are four FIFO's and each one sends data for one line. Therefore gate array B can input image data of five lines. Gate array B calculates the characteristic value of peripheral pixels according to the image data of five lines and the result is outputted to the address of the multi-function LUT. The multi-function LUT is the same one described in the shading correction. When the are separation mode is selected, the CPU reads the data for area separation from the EPROM (for data) and write into the multi-function LUT.

# [MTF correction]

When the characteristic value outputted from gate array B is inputted to the address of multi-function LUT, data which show the characteristics of the peripheral pixels are outputted from the multi-function LUT. For example, the data show that the pixel and the peripherals are characters and edged of line drawing or that they are part of a hatched image of photo in a newspaper or that they are part of a photo of continuous gradation (that is not a hatched photo). Filter process is performed according to each pixel's characteristics.

### [Gamma correction/line alignment/black-white highlight]

After the MTF correction, the image is subject to the gamma correction in order to cope with the OPC drum characteristics, the developing characteristics, and the actual copy density. Before copying, the CPU reads the density conversion look up table value corresponding to the value which was set by the user with the density adjustment key from the EPROM (data), and writes the data into the gamma correction LUT (SRAM). The image data are connected to the lower 8 bits of the gamma correction LUT address and converted by the look up table. Black-white highlight is performed at the same time.

### [Soft photo mode]

This is the multi-value dithering mode which has been newly added from this mode. The area gradation is combined with the pulse width modulation to improve the gradation of photo. The size of area gradation (dither matrix) can be selected with simulation.

### [Self printing mode]

Gate array B prints out the test pattern by outputting the address count values of main scanning and sub scanning.

# Gate array A

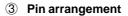

#### Pin arrangement table

| No.     | Pin name      | I/O    | Function                                                 |

|---------|---------------|--------|----------------------------------------------------------|

| 1       |               | 1/0    | r driction                                               |

|         | GND           | ~      |                                                          |

| 2       |               | 0      | Data bus to the peripheral memory                        |

| }<br>7  |               | }<br>0 | connected to this LSI.                                   |

| 8       | VDD           | •      |                                                          |

| 9       | RAMADR6       | 0      | Data bus to the peripheral memory                        |

| 10      | RAMADR7       | 0      | connected to this LSI.                                   |

| 11      | GND           |        |                                                          |

| 12      | RAMADR8       | 0      | Data bus to the peripheral memory connected to this LSI. |

| 13      | GND           |        |                                                          |

| 14      | VDD           |        |                                                          |

| 15      | RAMADR9       | 0      | Data bus to the peripheral memory                        |

| 2       | 2             | 2      | connected to this LSI.                                   |

| 20      | RAMADR14      | 0      |                                                          |

| 21      | FINAL         | 0      | Signal which shows the end of shading correction.        |

| 22      | GND           |        |                                                          |

| 23      | RAMADR0       | I/O    | Address bus to the peripheral memory                     |

| 2       | 2             | 2      | connected to this LSI.                                   |

| 30      | RAMADR7       | I/O    |                                                          |

| 31      | GND           |        |                                                          |

| 32      | XIFDAT0       | I/O    |                                                          |

| 2       |               | 2      | Data bus to set the built-in register.                   |

| 42      | XIFDAT7       | I/O    |                                                          |

| 43      | GND           |        |                                                          |

| 44      | SHADOUT0      | I/O    | Signal to output the data after shading                  |

| ∂<br>53 | ر<br>SHADOUT7 | 1∕O    | correction.                                              |

| 54      | GND           | 1/0    |                                                          |

| 54      | GND           |        |                                                          |

| No.      | Pin name   | I/O        | Function                                                         |  |

|----------|------------|------------|------------------------------------------------------------------|--|

| 55       | XIFADR0    | IN IN      | T difetion                                                       |  |

| 25       |            | )<br>      | Data bus to set the built-in register.                           |  |

| 60       | XIFADR5    | IN         |                                                                  |  |

| 61       | RAMRD      | OUT        | Read signal to the peripheral memory.                            |  |

| 62       | VDD        |            |                                                                  |  |

| 63       | GND        |            |                                                                  |  |

| 64       | WCLK       | OUT        | Not used.                                                        |  |

| 65       | CLK1       | IN         | System clock of this LSI. Clock of 16MHz is inputted.            |  |

| 66       | XIFEN      | IN         | Data enable signal to the built-in register.                     |  |

| 67       | XIFRD      | IN         | Data read signal to the built-in register.                       |  |

| 68       | XIFWR      | IN         | Data write signal to the built-in register.                      |  |

| 69       | RESET      | IN         | Initializes the LSI.                                             |  |

| 70       | VDD        | _          |                                                                  |  |

| 71       | CLK2       | IN         | System clock of this LSI. Clock of 16MHz is inputted.            |  |

| 72       | RAMWR      | OUT        | Write signal to the peripheral memory                            |  |

| 73       | HSYNC      | IN         | Image data 1 line read start signal.                             |  |

| 74       | PAGE       | IN         | Signal which shows the effective area of one page of image data. |  |

| 75       | RESERVE    |            |                                                                  |  |

| 76       | RESERVE    |            | Not used.                                                        |  |

| 77       | RESERVE    |            |                                                                  |  |

| 78       | RESERVE    |            | *                                                                |  |

| 79       | GND        |            |                                                                  |  |

| 80       | RESERVE    |            |                                                                  |  |

| 81       | RESERVE    |            | Not used.                                                        |  |

| 82       | RESERVE    |            |                                                                  |  |

| 83       | RESERVE    |            | *<br>*                                                           |  |

| 84       | GND        |            |                                                                  |  |

| 85       | H0         | OUT        |                                                                  |  |

| 2        | ~          | )<br>All T | Not used.                                                        |  |

| 87       | H2         | OUT        |                                                                  |  |

| 88       | VDD        |            |                                                                  |  |

| 89       | GND        | 0.17       |                                                                  |  |

| 90<br>〉  | V0<br>2    | OUT<br>2   | Not used.                                                        |  |

| ∂<br>92  | (<br>V2    | OUT        |                                                                  |  |

| 93       | ADIN0      | IN         |                                                                  |  |

| 2<br>100 | ک<br>ADIN7 | N          | Image data bus                                                   |  |

# Gate array B

# Pin arrangement table

| No.           | Pin name      | I/O       | Function                                                                   |

|---------------|---------------|-----------|----------------------------------------------------------------------------|

| 1             | GND           |           |                                                                            |

| 2             | VCC           |           |                                                                            |

| 3             | AIN0          | IN        |                                                                            |

| 2             | 2             | 2         | (n) Line image data input pin.                                             |

| 10            | AIN7          | IN        |                                                                            |

| 11            | RAMADR0       | OUT       | Signals according to each mode<br>such as the result of area separation    |

| 14            | ک<br>RAMADR3  |           | are outputted to the external LUT                                          |

| 14            | RAMADR3       | OUT       | from this pin.                                                             |

| 15            | GND           |           |                                                                            |

| 16            | RAMADR4       | OUT       | Signals according to each mode                                             |

| 2             | 2             | 2         | such as the result of area separation<br>are outputted to the external LUT |

| 19            | RAMADR7       | OUT       | from this pin.                                                             |

| 20            | VCC (fixed)   |           |                                                                            |

| 211           | GND (fixed)   |           |                                                                            |

| 22            | GND           |           |                                                                            |

| 23            | BIN0          | IN        |                                                                            |

| 20            |               | 2         | (n+1)the line image data input pin                                         |

| 30            | BIN7          | IN        | Notusod                                                                    |

| 31            | RESERVED      |           | Not used.                                                                  |

| 32            | RAMADR8       | OUT       | Signals according to each mode<br>such as the result of area separation    |

| ∂<br>34       | ک<br>RAMADR10 | }<br>OUT  | are outputted to the external LUT                                          |

| 54            | RAMADRIO      | 001       | from this pin.                                                             |

| 35            | GND           |           |                                                                            |

| 36            | RAMADR11      | OUT       | Signals according to each mode                                             |

| 2             | 2             | 2         | such as the result of area separation<br>are outputted to the external LUT |

| 39            | RAMADR14      | OUT       | from this pin.                                                             |

| 40            | GND           |           |                                                                            |

| 41            | RAMDATA0      | IN        | Pin for data input from the external                                       |

| 48            | ر<br>RAMDATA7 |           | LUT.                                                                       |

| 40            | FILOUT0       | OUT       |                                                                            |

| ~             |               | $\sim$    | Pin for output of the result of filter                                     |

| 52            | FILOUT7       | OÙT       | process.                                                                   |

| 53            | GND           |           |                                                                            |

| 54            | FILOUT4       | OUT       | Pin for output of the result of filter                                     |

| 57            | ر<br>FILOUT7  | V<br>OUT  | process.                                                                   |

|               |               |           | Clock signal input pin. Clock of                                           |

| 58            | CLK1          | IN        | 16MHz is inputted.                                                         |

| 59            | GND           |           |                                                                            |

| 60            | VCC           |           |                                                                            |

| 61            | GND (fixed)   |           |                                                                            |

| 62            | VCC (fixed)   |           |                                                                            |

| 63            | CIN0          | IN        |                                                                            |

| 2             | ک<br>CIN7     | ≀N        | (n+2)the line image data input pin                                         |

| 70<br>71      | XIFDAT0       | IN<br>I/O |                                                                            |

| $\mathcal{L}$ |               | 2         | Data bus to set the built-in register.                                     |

| 78            | XIFDAT7       | I/O       |                                                                            |

| 79            | GND           |           |                                                                            |

| 80            | DIN0          | IN        |                                                                            |

| ∂<br>87       | ک<br>DIN7     | ≀N        | (n+3)the line image data input pin                                         |

| 88            | RESET         | IN        | Reset signal of the LSI                                                    |

| 89            | XIFADR0       | IN        | -                                                                          |

| 2             |               | lin<br>Z  | Address bus to select the built-in                                         |

| 94            | XIFADR5       | IŇ        | register.                                                                  |

| No.        | Pin name                 | I/O      | Function                                                             |

|------------|--------------------------|----------|----------------------------------------------------------------------|

|            |                          |          | Signal showing the effective image                                   |

| 95         | AREALDLY                 | OUT      | area which is behind from AREA signal by 4 clocks. LOW active.       |

| <u> </u>   |                          |          | Clock signal input pin. Clock of                                     |

| 96         | CLK2                     | IN       | 16MHz is inputted.                                                   |

|            |                          |          | Data read signal to the built-in                                     |

| 97         | XIFRD                    | IN       | register.<br>LOW active.                                             |

|            |                          |          | Data write signal to the built-in                                    |

| 98         | XIFWR                    | IN       | register. LOW active.                                                |

| 99         | XIFEN                    | IN       | Data enable signal to the built-in                                   |

|            |                          |          | register. LOW active.                                                |

| 100        | VCC (fixed)              |          |                                                                      |

| 101<br>102 | GND (fixed)<br>BUNRIOUT0 | OUT      |                                                                      |

| ~          |                          | 2        | Area separation test pin.                                            |

| 105        | BUNRIOUT3                | оùт      |                                                                      |

| 106        | GND                      |          |                                                                      |

| 107        | BUNRIOUT4                | OUT      |                                                                      |

| 112        | ک<br>BUNRIOUT9           | _        | Area separation test pin.                                            |

| 113        | GND                      | 001      |                                                                      |

|            | -                        | INJ      | Clock signal input pin. Clock of                                     |

| 114        | CLK3                     | IN       | 16MHz is inputted.                                                   |

| 115        | ZOOMIN0                  | IN       |                                                                      |

| 125        | ر<br>ZOOMIN10            | _        | Zooming process data input pin.                                      |

| 126        | GND                      |          |                                                                      |

| 127        | ZOOMOUT0                 | IN       |                                                                      |

| 2          | 2                        | 2        | Zooming process data input pin.                                      |

| 130        | ZOOMOUT3                 | IN       |                                                                      |

| 131<br>132 | GND<br>ZOOMOUT4          | IN       |                                                                      |

| 132        | 2001/0014<br>2           | lin<br>2 | Zooming process data input pin.                                      |

| 135        | ZOOMOUT7                 | ÌŇ       |                                                                      |

| 136        | GND                      |          |                                                                      |

| 137        | VCC                      |          |                                                                      |

| 138        |                          | IN       | Zooming process data issut siz                                       |

| ر<br>140   | ZOOMOUT10                | ≀N       | Zooming process data input pin.                                      |

| 141        | FIFOWEN                  | OUT      | Write enable signal to the line                                      |

|            |                          | 001      | memory. LOW active.                                                  |

| 142        | VCC (fixed)              |          |                                                                      |

| 143        | GND (fixed)              |          |                                                                      |

| 144        | GND                      |          | Pood onable signal to the line                                       |

| 145        | FIFOREN                  | OUT      | Read enable signal to the line<br>memory. LOW active.                |

| 146        | RAMDLY0                  | OUT      |                                                                      |

| 2          |                          | )<br>∧   | 10-clock behind signal of<br>RAMDATA0 ~ 2.                           |

| 148        | RAMDLY2                  | OUT      |                                                                      |

| 149        | AREAHDLY                 | OUT      | Signal showing the effective image<br>area which is behind from AREA |

|            |                          |          | signal by 5 clocks. LOW active.                                      |

| 150        | HSYNC                    | IN       | Image data 1 line scanning start                                     |

|            |                          |          | signal                                                               |

| 151        | AREA                     | OUT      | Signal which shows the effective<br>image area. LOW active.          |

| 152        | EIN0                     | IN       |                                                                      |

| 2          | 2                        | 2        | (n+4)the line image data input pin.                                  |

| 159        | EIN7                     | IN       |                                                                      |

| 160        | PAGE                     | IN       | Signal which shows one page of<br>image data. LOW active.            |

| L          |                          |          | mage data. LOW abiive.                                               |

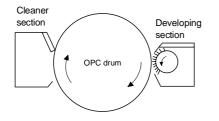

# [2] PROCESS SECTION

# (OPC drum, cleaning unit)

# 1. Outline

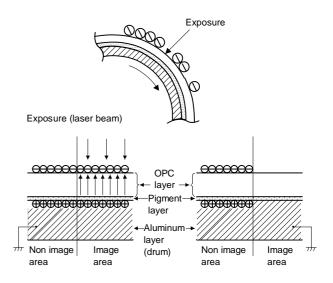

The indirect electrostatic copiers use normal paper for copying, and form electrostatic latent images on the OPC drum surface which can be used repeatedly, develop them into visible images (toner images), and transfer them on copy paper. Copies are made indirectly in the copier of this type.

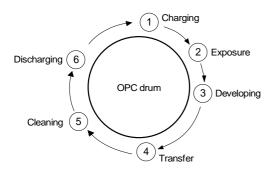

The PPC (Plain Paper Copier) makes copies in six processes: charging, exposure, developing, transfer, discharging, and cleaning which cleans the OPC drum surface to use is repeatedly after transfer.

# (1) Image forming process

- 1 The OPC drum is charged.

- 2 The OPC drum is exposed to form electrostatic latent images.

- ③ Toner is attracted to the electrostatic latent images.

- ④ The developed toner images are transferred on recording media such as paper.

- (5) Residual toner remaining on the OPC drum surface is cleaned.

- 6 Residual charges on the OPC drum are removed.

# (2) OPC drum

Some materials conduct electricity, and some others do not. The materials are divided into three groups according to their conductivity: conductors, semiconductors, and insulators.

This classification is not strict, and it is difficult to classify the materials strictly.

Generally speaking, the materials with resistivity of  $10^8 \ \Omega$  cm or above are called insulators. Those with resistivity of  $10^{-3} \ \Omega$  cm or below are called conductors.

The materials between the two are generically called semiconductors. The conductors are always conductive. The semiconductors are normally not conductive, but under a certain condition become conductive.

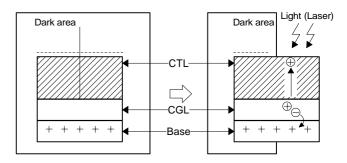

The photoconductor used in the copiers are insulators when they are not exposed with light, and reduce the resistivity when they are exposed with light, that is, they become conductive (by the photo conductivity phenomenon) when exposed with light. They are also called as photo semiconductors and used in the copiers.

Principle of photoconductor (conductivity)

### (3) Kinds of photoconductors

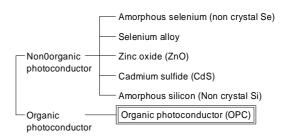

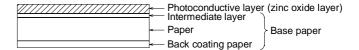

Major photo conductive materials used in the copiers are zinc oxide (ZnO), amorphous selenium (amorphous Se) alloy, cadmium sulfide (CdS), amorphous silicon (amorphous Si), and organic photoconductor (OPC).

The compositions of photoconductors used in the copiers are shown below.

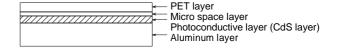

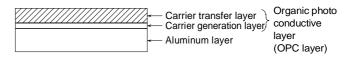

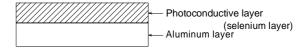

Zinc oxide (ZnO) master

Cadmium sulfide (CdS) drum

Organic photoconductor (OPC) master or drum

#### Selenium (Se) drum)

#### Characteristics of organic photoconductors (OPC)

- · Can be formed into various shapes (drum, sheet, belt)

- High insulation in a dark place. (Acceptability and retainability of charges)

- Light weight

- · Stable against humidity and temperature

- Safe and clean to the environment (harmless)

- Weak in wear by friction

- Weak in durability against light and ozone

### (4) Characteristics of photoconductors

The important characteristics of photoconductors are as follows:

- 1. Photo sensitivity

- Spectrum characteristics

Charge retainability

- Acceptance potential

Residual potential

- 6. Fatigue

#### [Photo sensitivity]

It is determined by the attenuation speed of the potential when exposed with light.

#### [Spectrum characteristics]

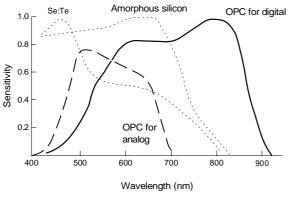

The sensitivity of photoconductors differs depending on the kind and the waveform of light.

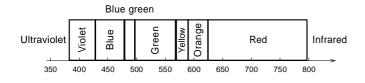

Spectrum sensitivity

#### Relationship between color and waveform

Human eyes can feel the lights with waveform of 380nm to 780nm.

These are called "Visible lights." The light whose waveform is shorter than that is called "Ultraviolet light." The light whose waveform is longer than that is called "Infrared light."

The figure below shows the relationship between lights and waveforms.

#### [Acceptance potential]

The dark resistance of the photoconductor layer decreases as the electric field applied between layers increases.

When the photoconductor is charged, the electric field is formed to a high level and the resistance of the layer decreases to restrict the charging amount of the photoconductor. The potential of the photoconductor at that time is called the acceptance potential, which serves as an important factor to determine the potential contrast. The photoconductor is generally charged to a potential slightly lower than the acceptance potential in order to avoid applying an electrical strain to the photoconductor.

#### [Charge retainability]

The retaining time of electrostatic latent images on the photoconductor is determined by the speed of decrease in the potential in a dark place. That is, it is measured with the time for the photoconductor potential to decrease to the half of the initial level. This retainability of electrical charge makes a problem when the interval time between exposure and developing is longer. In the machines where a series of operations of charging, exposure, and developing are automated, the interval between the processes is short enough and there is no problem.

#### [Residual potential]

When the charged photoconductor is exposed, the potential is rapidly attenuated at first then slowly. The potential where this slow attenuation starts is called the residual potential. The lower the residual potential is, the greater the voltage contrast is. Therefore, the lower residual potential is desirable.

#### [Fatigue]

When the photoconductor is charged and exposed repeatedly, it is fatigued. Fatigue of the photoconductor results in increase in attenuation speed of the photoconductor potential and decrease in the retainability of charges.

In the above, the necessary characteristics for the photoconductors are described. In an actual machine, when charging is repeated by the charger, dust and dirt or splashed toner may be attached to the saw tooth. These are not resulted from uneven charging, and they should be removed by cleaning.

# 2. Basic process and composition

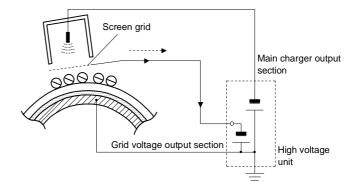

This machine employs the scorotron system to charge the photoconductor surface uniformly to a certain level. The conventional corona charger mechanism is employed which is composed of the corona wire and the saw tooth plate (stainless plate of 0.1mm thick).

In corona charging, oxygen molecules in the air are ionized to form ozone. This mechanism suppresses the generation of ozone.

- The process separation mechanism is employed for serviceability.

- The one-touch stopper mechanism prevents against high voltage leakage caused by drop of the corona charger unit.

# (1) Details of image forming process

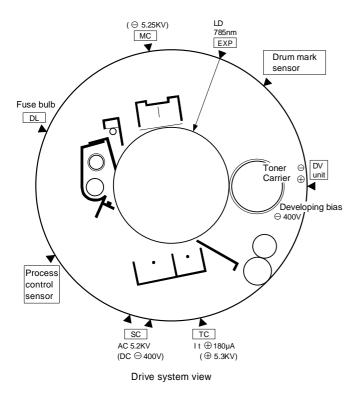

## Step 1: Charging

Main charger high voltage transformer (MHVG)

|               | Grid voltage | Developing bias voltage |

|---------------|--------------|-------------------------|

| Standard mode | -490V        | -400V                   |

| Photo mode    | -490V        | -400V                   |

| TSM mode      | -440V        | -350V                   |

| Printer mode  | -460V        | -400V                   |

A uniform negative charge is applied to the OPC drum surface by negative corona discharge of the main charger.

The OPC drum surface potential is controlled by the screen grid voltage to be virtually the same level as the grid voltage.

- When the drum surface potential is lower than the grid voltage, electric charges generated by discharging of the main charger are passed through the screen grid to keep charging until the drum surface potential reaches the same level as the grid voltage.

- When the drum surface potential reaches about the same level as the grid voltage, electric charges generated by discharging of the main charger flow through the electrode of the screen grid to the high voltage unit grid voltage output circuit. Therefore the drum surface potential is kept at the same level as the grid voltage.

### Step 2: Exposure (laser beams)

Laser beams are generated in the LSU according to the print signal from the ICU and radiated to the drum surface. The resistance of the are of OPC layer where laser beams are radiated reduces to discharge negative charges, forming electrostatic latent images on the drum surface.

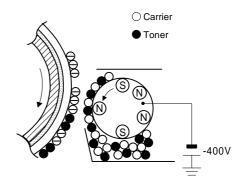

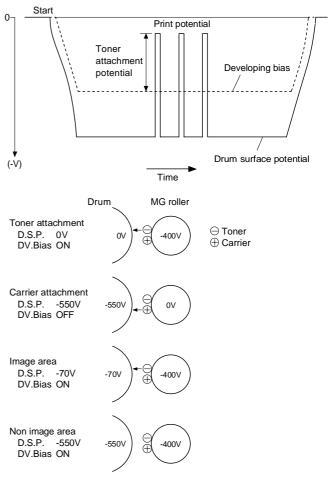

### Step 3: Developing (Bias -400V)

The electrostatic latent images on the drum surface are made visible images. This model uses the two-component magnetic brush developing system to supply the bias voltage of -400V to carriers (MG roller), and toner is negatively charged by friction with carriers.

Since the non-image area on the drum is negatively charged greater than the developing bias, the negatively charged toner is repulsed from the drum. The image area on the drum is exposed by laser beams and its potential is decreased. Then negative toner is attached to it by the DV bias.

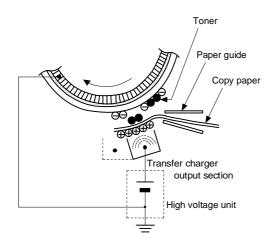

### Step 4: Transfer

The visible images on the drum surface are transferred to copy paper. Positive corona of the transfer charger is applied to the back of the copy paper to transfer toner on the drum to the copy paper.

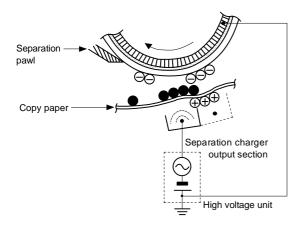

### **Step 5: Separation**

Since the copy paper is positively charged and the drum is negatively charged after transfer, an attraction force is generated between the drum and the copy paper. Then an AC corona overlapped with negative DC is applied to the copy paper to decrease the copy paper potential to the same level as the drum surface potential. Therefore an attraction force between the drum and the copy paper disappears, and the copy paper is separated by its own flexibility. If the paper is not separated by the separation charger, it is forcibly separated by the separation pawl.

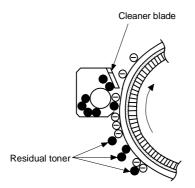

### Step 6: Cleaning

Residual toner on the drum is removed by the cleaning blade.

### Step 7: Discharge

The discharge lamp light is radiated to the drum to reduce the electric resistance of the OPC layer, eliminating the residual charges.

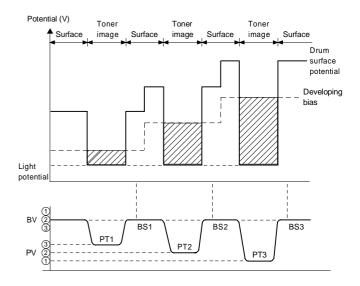

(3) Potential transition of the DV unit section

DSP: Drum surface potential

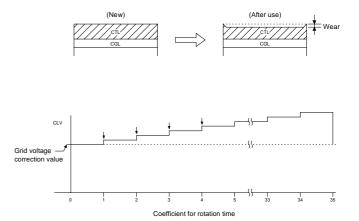

## (4) OPC drum sensitivity reduction correction

In the AR-5132, deterioration of copy quality is prevented by correction with the charging grid voltage against the potential reduction of the OPC drum due to repeated use.

The drum wear increases the grid voltage to maintain the drum surface potential at a constant level, and the apparent sensitivity of the OPC drum is decreased. To correct this, the laser beam strength is increased when the coefficient of the drum rotating time for correction of the charging grid voltage reaches a certain level.

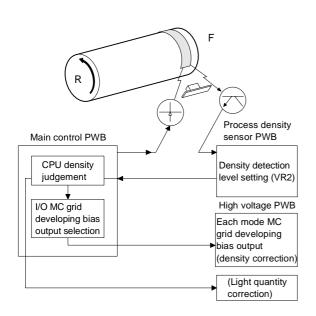

# (5) Process control function

### [Outline]

The density of the reference toner image formed on the OPC drum surface is used as the standard patch density, and the developing bias and the charging grid voltage are controlled to provide the same density as the standard patch density for stabilizing the copy images.

That is, the process conditions are set, and the high voltage output is changed and corrected so that the toner density is stabilized under the conditions.

#### **Process control**

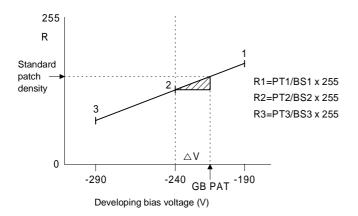

Toner patch images are formed on the OPC drum surface under the three kinds of conditions (MC grid bias voltage) and the developing bias. (The voltage is an actually measured value.)

In the process control, toner patch images are formed at the laser output of the reference grid voltage (-410V) and the developing bias (-240V)  $\pm 50V$  and duty of 100%.

② The three kinds of toner patch images and the drum surface are measured with the process density sensor to obtain the relationship between them.

③ The developing bias voltage is obtained from comparison with the standard patch density.

In the AR-5132, the absolute value of the density sensor output value is not directly used for the control calculation, but the ratio of the drum surface sensor output value (BSn) and the toner patch image sensor output value (PTn) is used for the control calculation.

Since the ratio of PTn/BSn) is not affected by the change in the absolute value of the light quantity of the reflection type sensor due to dirt or deterioration, stable control is performed.

④ In the developing bias/MC grid voltage correction, the value of △V of the developing bias voltage calculated with the standard patch density and the process control is fed back to the bias voltage and the MC grid voltage in each mode.

When the developing bias voltage is corrected, the corresponding MC grid bias is calculated and controlled.

(5) When a value reaching the reference level is not obtained in a series of control procedures, the patch forming conditions are shifted toward the reference level side and repeat the series of control procedures. The repetition is allowed for max. five times.

#### LD power correction

The LD power correction is performed depending on the result of the developing bias voltage calculation. When the correction width  $\triangle V$  of the developing bias voltage becomes greater, the MC grid voltage is corrected accordingly. If the LD power is the same at that time, the apparent sensitivity of the OPC drum is changed. To correct this, the LD power is made greater when the developing bias voltage is increased; on the contrary the LD power is made smaller when the developing bias voltage is decreased. The width of decrease or increase is determined according to the built-in table. This correction stabilizes half tone prints.

#### **Process control timing**

In the AR-5132, the process control is performed at the following timing.

- a. When the power switch is turned on. (during warming up)

- b. When the accumulated copy time reaches 30 min, the process control will be made in the next copying.

- c. When the standby time reaches 1 hour, the process control will be made in the next copying.

- d. When simulation 46 is executed.

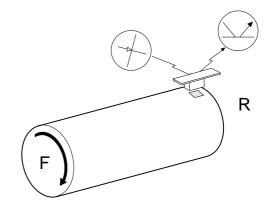

#### Drum marking

In the AR-5132, toner patch images are formed at the same position on the OPC drum to improve accuracy of the process control.

That is, a marking is provided on the drum, and the marking point is sensed and toner patch images are formed at a certain position.

If the marking is not sensed, the copy density is extremely reduced.

# [3] DEVELOPING SECTION

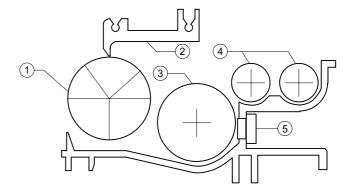

# 2. Basic composition

# 1. Basic outline

## (1) Two-component developer

Developer is composed of tow components; toner and carrier.

Carrier functions as a media to attract toner to electrostatic latent images on the OPC drum.

As the toner is mixed with the carrier, the friction changes it to positive or negative.

Developer characteristics changes due to deterioration to degrade print quality. Therefore developer must be replaced periodically.

### (2) Two-component magnetic brush developing

A rotatable non-magnetic sleeve is provided on the magnet roller and rotated.

Carrier forms a magnetic brush on the sleeve surface by the magnetic force to attract toner to electrostatic latent images on the OPC drum.

# (3) Developing bias

Since the reverse developing system is employed, toner is attracted to the area (light potential area) where laser beams are radiated. Though it is the light potential area, the OPC drum is negatively charged. To attract negatively charged toner to the OPC drum, a higher (absolute value) bias must be applied to the MG roller. Therefore, the amount of attracted toner can be varied by the level of the developing bias voltage.

The developing bias serves to prevents against attachment of excessive toner by setting it lower (in absolute value) than the surface potential (dark potential) when making white background.

| -   |                                    |                                                                                     |

|-----|------------------------------------|-------------------------------------------------------------------------------------|

| No. | Name                               |                                                                                     |

| 1   | Developing magnet roller           | Forms the magnetic brush of carrier by the magnetic force.                          |

| 2   | Developing doctor blade            | Used of regulation of the<br>magnetic brush height.                                 |

| 3   | Developing stirring roller         | Stirs carrier in the developing unit to distribute toner uniformly.                 |

| 4   | Developing transport roller        | Transports toner supplied from<br>the toner hopper unit to the<br>stirring section. |

| 5   | Developing toner density<br>sensor | Detects the toner density in the developer.                                         |

# 3. Basic operation

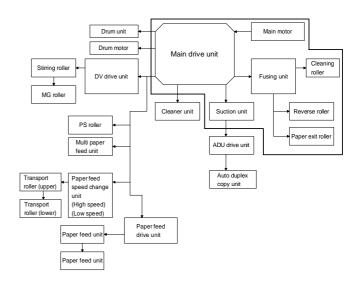

When the power switch of the machine is turned on, the machine starts warming up. After about one minute, the main motor rotates.

The drive power of the developing unit is transmitted from the main motor through the main drive unit to the developing drive unit.

Change in the mixing ratio of toner and carrier is sensed by the toner density sensor in the developing unit as the change in magnetic permeability, and outputted to the analog input pin of the main PWB CPU of the main body.

The CPU monitors the input voltage level, and controls the main motor and toner motor to supply, transport, and stir toner until the proper density is obtained.

# [4] PAPER FEED SECTION

# 2. Basic composition

# 1. Basic outline

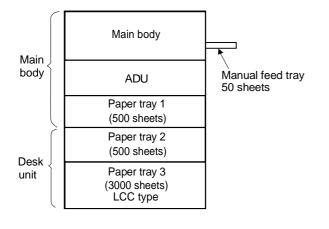

The AR-5132 employs the font loading system and the multi paper feed table which can be stored inside the machine, cutting the installation space. It is also equipped with the two-step trays, the 3000sheet LCC tray, and the manual paper feed tray which allows continuous feeding of 50 sheets as standard provisions.

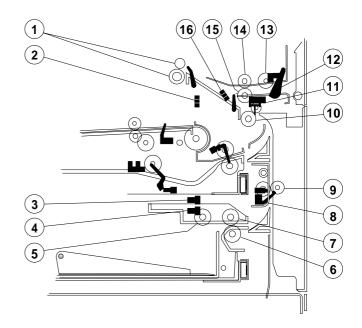

| No.  | Name                              | Function, operation                                                                    |  |

|------|-----------------------------------|----------------------------------------------------------------------------------------|--|

| 1    | Resist roller                     | Makes synchronization between paper and images by control of the resist roller clutch. |  |

| 2    | (PPD2)<br>Paper transport sensor  | Used to control the transport roller clutch (TRC).                                     |  |

| 3    | (LUD3)<br>Lift upper limit sensor | Used to control the lift-up motor. Stopped at HIGH.                                    |  |

| 4    | (PED3)<br>Paper empty sensor      | Used to detect paper empty.                                                            |  |

| (5)  | Pick-up roller                    | Picks up paper and falls simultaneously with turning on the paper feedf solenoid.      |  |

| 6    | Paper feed separation roller      | Preents agaisnt multi paper feed.                                                      |  |

| Ø    | Paper feed roller                 | Paper feed roller for the paper tray 1, (Includes the one-way clutch.)                 |  |

| 8    | (PID)<br>Paper entry sensor       | Detects pper entry from the paper tray 1 and turns off the paper feed solenoid.        |  |

| 9    | Transport roller                  | Transports paper from the paper tray 1.                                                |  |

| (10) | Transport roller                  | Transoprts paper from the cassette to the resist roller.                               |  |

| 1    | (TFD)<br>Wast toner fll sensor    | Full at LOW.                                                                           |  |

| 12   | (PED1)<br>Paper empty sensor      | Detects paper empty in the manual paper feed mode. Paper present at LOW.               |  |

| 13   | Pick-up roller                    | Manual feed peper pick-up roller.                                                      |  |

| (14) | Paper feed roller                 | Manual paper feed roller (Includes the one-way clutc.)                                 |  |

| (15) | Paper separation roller           | The manual paper feed separation roller prevents agaist multi paper feed.              |  |

| 16   | (PPD1)<br>Paper transport sensor  | Detects paper entry from the main body or the desk.                                    |  |

# 3. Basic operation

# (1) Manual paper feed section operations

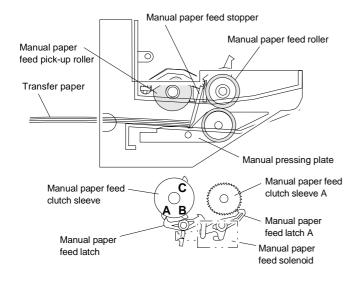

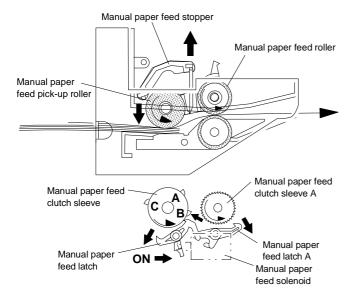

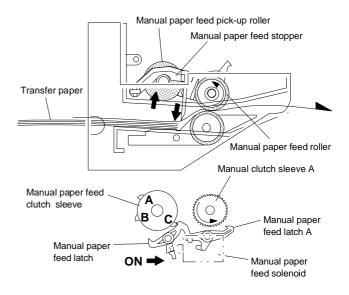

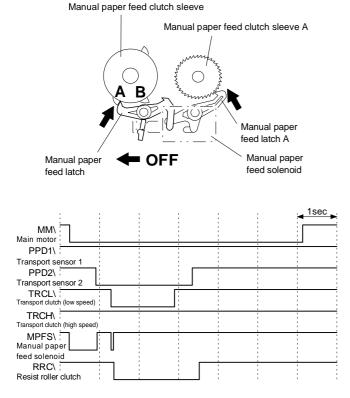

① Before the operation of the manual paper feed section, the manual paper feed solenoid (MPFS) is OFF and the manual paper feed stopper is closed and the paper pick-up roller is up. The latch and the clutch are at positions as shown in the table below.

② When the start button is pressed, the manual paper feed solenoid (MPFS) is turned on, and the manual paper feed latch A is disengaged from the manual paper feed clutch sleeve A, and the manual paper feed roller and the manual paper feed pick-up roller rotate. At the same time, the manual paper feed stopper is opened and the manual paper feed pick-up roller is pressed on the paper to start paper feed.

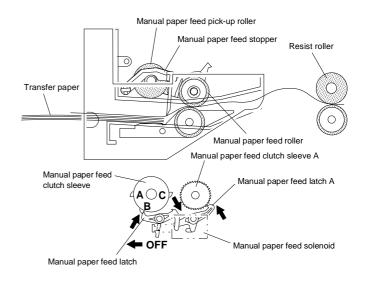

③ When the manual paper feed clutch sleeve pawl C is caught by the manual feed latch, the manual fed stopper falls and the manual feed pick-up roller rises. At the time, the transport roller is rotating.

④ When the tip of the transferred paper is detected by PPD2, the manual paper feed solenoid is turned off after about 0.2 sec. At that time, the clatch sleeve pawl B is caught by the manual paper feed latch.

As a result, the paper is warped between the resist roller and the paper feed roller.

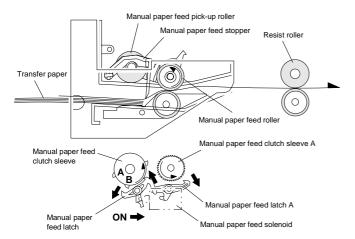

(5) The manual paper feed solenoid is turned on for 0.08 sec in synchronization with rotation of the resist roller, and the manual peper feed roller is rotated. Therefore, paper jams due to insufficient pick-up of the resist roller is prevented.

At that time, the manual paper feed pick-up roller remains up.

(6) The manual paper feed solenoid is turned off and the clutch sleeve pawl A is caught by the manual paper feed latch and the mamual paper feed is completed.

Manual paper feed timing chart

### (2) Cassette paper feed section operations

The cassette paper feed operations are the same in the paper tray 1 and the paper tray 2.

The following descriptions are based on the paper tray 1.

1 Lift up

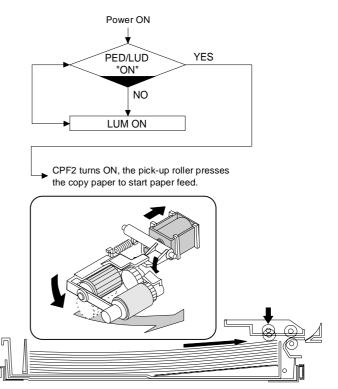

When the power is turned on, the main circuit checks the sensors.

The lift up motor is turned on/off to make ready for paper feed according to the states of the paper empty sensor (PED) and the lift-up senosr (LUD).

#### 2 Paper feed

When the start button is pressed, the cassette paper feed solenoid (CPFS2) and the cassette paper feed roller clutch (CPFC2) are turned on. By turning on the solenoid, the paper feed pick-up roller is pressed down to press the paper.

By turning on the clutch, the paper feed roller and the pick-up roller start the paper feed operation.

The fed paper is passed through the paper entry sensor (PID) to the transport roller.

the transport roller is rotated by two drive clutches. For transport from the paper feed section to the resist roller, It is driven by the high speed clutch. The resisted paper is transported to the process section in synchronization with the optical system. The transport speed at that time is switched from the high speed clutch to the low speed clutch so that the transport speed becomes the same as the process rotating speed.

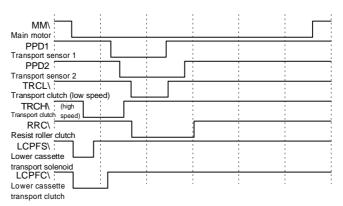

#### Lower cassette paper feed timing chart

# [5] TRANSPORT AND FUSING SECTIONS

# 1. Outline

The AR-5132 allows paper transport of max. A3 (11"  $\times$  17") to min. A5 (8 1/2"  $\times$  5 1/2").

After transfer of images, the paper is separated from the drum and transported to the fusing section by rotation of the resist roller and the transport belt.

The transport section is provided with the separation sensor (PSD). This sensor detects separation of paper and is used for taking the drive timing of the duplex gate solenoid (DGS) after fusing.

# 2. Basic composition and functions

# (1) Transport section

① Transport belts (2 pcs.)

The transport belts are corrugated to push the rear edge of paper.

2 Separation sensor (PSD)

This is a transmission type photo sensor and is attached to the chassis of the main body.

③ Suction fan motor and ozone filter

Ozone generated in the process high voltage section is absorbed by the filter.

# (2) Fusing section

1 Upper heat roller

This roller is teflon-coated in the shape of a reversed crown.

2 Lower heat roller

This roller is a silicon rubber roller in the shape of a crown.

3 Upper cleaning roller

This roller, impregnated with silicon oil, is used to remove dirt from the upper heat roller to provide better separation of paper and lengthens the life of the heat roller.

④ Separation pawl

Four separation pawls which are teflon-coated are used for the upper heat roller for reducing friction.

Two separation pawls are used for the lower heat roller.

5 Upper/lower separation function

The upper heat roller section and the lower heat roller section can be separated from each other for better serviceability.

6 Division of the drive system

The fusing unit is driven by the main drive unit. Since the fusing section is manually fed in case of a paper jam, a spring clutch is provided in the main drive gear to prevent that an excessive load is applied to the gears.

# [6] HIGH VOLTAGE SECTION

# 1. Outline

There are three kinds of chargers; the main charger, the transfer charger, and the separation charger. The main charger employs the scorotron system. The drum surface is charged negatively and uniformly by electric charges controlled by the screen grid which is positioned between the charger and the drum.

The transfer charger is used to transfer toner images which are on the drum to the copy paper. A negative high voltage is applied to the back of the copy paper.

The separation charger applies AC corona to the copy paper to eliminate a potential difference between the drum in order to perform separation.

# 2. Basic composition

## (1) Main charger high voltage transformer (MHVG)

|               | Grid voltage | Developing bias<br>voltage |

|---------------|--------------|----------------------------|

| Standard mode | -490V        | -400V                      |

| Photo mode    | -490V        | -400V                      |

| TSM mode      | -440V        | -350V                      |

| Printer mode  | -460V        | -400V                      |

# (2) Transfer charger high voltage transformer (THVG)

+13.5µA (Electrode sheet front/rear balance difference: within 3µA)

# (3) Separation charger high voltage transformer (SHVG)

DC component voltage: -400±10V

# [7] RADF MECHANISM SECTIONS

# 1. Operation flowchart

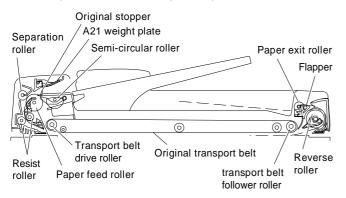

The figures below show the transport path of an document from the document setting, through paper feed, copying, to paper exit. For details of operations, refer to the operation process.

# 1) RAD mode (duplex copy mode) copying

|     | START<br>↓                        |                                                                                                                                                                         |

|-----|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | Step 01:<br>↓                     | The transport section is closed. (AUOD ON)                                                                                                                              |

|     | Step 02:                          | An document is set on the document tray.<br>(DSS output HIGH)                                                                                                           |

|     | Step 03:<br>↓                     | Document feed display ON                                                                                                                                                |

|     | Step 04:<br>↓                     | Print SW ON                                                                                                                                                             |

|     | (Preliminary<br>paper feed):<br>↓ | <ul> <li>* A: For the first document, dummy paper<br/>exit is performed.</li> </ul>                                                                                     |

| * A | Step 05:                          | Paper feed motor (DFM) forward rotation<br>(Paper feed roller, semi-circular roller<br>rotation)<br>Since the stopper is up, paper feed is not<br>performed.            |

|     | Step 06:                          | Reverse motor (DRM) forward rotation<br>(Reverse roller, paper exit roller rotation)                                                                                    |

|     | Step 07:                          | <ul> <li>Transport motor (DTM) rotation</li> <li>(Transport belt rotation)</li> <li>* B: If there has been an document on the tray, is discharged.</li> </ul>           |

| * A | Step 08:                          | Paper feed motor (DFM) OFF<br>Paper feed solenoid (DFSOL) ON<br>(The weight plate and the stopper move down<br>to press the document onto the semi-circular<br>roller.) |

|     | Step 09:                          | Paper feed motor (DFM) forward rotation<br>(Paper feed roller, semi-circular roller<br>rotation)<br>The document feed is started.                                       |

|            | $\downarrow$                      |                                                                                                                                                    |

|------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| * B        | Step 10:                          | Reverse sensor (RDD) senses the lead edge<br>of the discharged document.<br>(RDD output HIGH)                                                      |

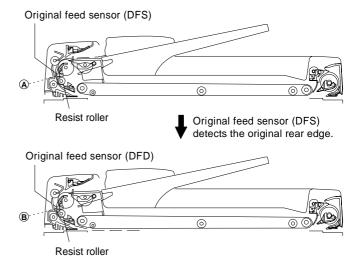

|            | Step 11:                          | Document feed sensor (DFD) senses the lead edge of the discharged document. (DFD output HIGH)                                                      |

|            | Step 12:                          | Paper feed motor (DFM) OFF<br>The document is stopped by the resist roller.                                                                        |

|            | Step 13:                          | Paper feed motor (DFM) reverse rotation<br>(Resist roller rotation)<br>The lead edge of the document is taken up by<br>the resist roller.)         |

|            | Step 14:                          | Document width sensor (DWS) senses the document width. (Output LOW)                                                                                |

|            | Step 15:                          | Document timing sensor (DTD) senses the lead edge of the document. (DTD output HIGH)                                                               |

|            | Step 16:                          | Paper feed motor (DFM) OFF<br>(The document is stopped with its lead edge<br>taken up by the resist roller.)                                       |

| * B        | Step 17:                          | Reverse sensor (RDD) senses the rear edge<br>of the discharged document. (RDD output<br>LOW)<br>Reverse motor (DRM) rpm down                       |

|            | Step 18:                          | Transport motor (DTM) OFF<br>(Transport stop)                                                                                                      |

| <b>*</b> B | Step 19:                          | Document discharge                                                                                                                                 |

|            | Step 20:                          | Reverse motor (DRM) OFF<br>(Reverse roller, paper exit roller stop)<br>(Paper feed reverse)                                                        |

|            | (Preliminary<br>paper feed):<br>↓ |                                                                                                                                                    |

|            | Step 21:                          | Transport motor (DTM) forward rotation<br>Transport motor, reverse motor (DRM)<br>forward rotation (Reverse roller, paper exit<br>roller rotation) |

|            | Step 22:                          | Paper feed motor (DFM) reverse rotation<br>(Resist roller rotation)<br>The document is sent to the transport section.                              |

|            | Step 23:                          | Document feed sensor (DFD)<br>Senses the rear edge of the discharged<br>document. (DFD output LOW)                                                 |

T

| * C Step 24:                | <ul> <li>Paper feed solenoid (DFSOL) OFF</li> <li>(The weight plate and the stopper move up.)</li> <li>* C: If there is no document on the document tray, move up the stopper and the weight plate.</li> </ul> | Step 38:           | Paper feed motor (DFM) forward rotation<br>(Paper feed roller, semi-circular roller<br>rotation)<br>The document feed is started.                             |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                             |                                                                                                                                                                                                                | Step 39:           | Document feed sensor (DFD) senses the<br>lead edge of the document.<br>(DFD output HIGH)                                                                      |

| Step 25:                    | Document width sensor (DWS) output HIGH                                                                                                                                                                        | ↓<br>↓             |                                                                                                                                                               |

| Step 26:                    | Document timing sensor (DTD) senses the rear edge of the document.<br>(DTD output LOW)                                                                                                                         | Step 40:           | Paper feed motor (DFM) OFF<br>The document is stopped by the resist roller.                                                                                   |

|                             | Paper feed motor (DFM) OFF (Resist roller<br>stop)<br>Reverse solenoid (DRSOL) ON (The flapper<br>move up.)                                                                                                    | Step 41:           | Paper feed motor (DFM) forward rotation<br>(Resist roller rotation)<br>The lead edge of the document is taken up<br>by the resist roller.                     |

| Step 27:                    | Reverse sensor (RDD) senses the lead edge of the document. (RDD output HIGH)                                                                                                                                   | Step 42:           | Document width sensor (DWS) senses the document width. (Output LOW)                                                                                           |

| Step 28:                    | The lead edge of the document is moved counterclockwise by the flapper.                                                                                                                                        | Step 43:<br>↓      | Document timing sensor (DTD) senses the<br>lead edge of the document. (DTD output<br>HIGH)                                                                    |

| Step 29:<br>↓               | Transport motor (DTM) OFF<br>(Transport belt stop)                                                                                                                                                             | Step 44:           | Paper feed motor (DFM) OFF<br>(The document is stopped with its lead edge<br>taken up by the resist roller.)                                                  |

| Step 30:                    | Reverse motor (RDM) OFF<br>(Reverse roller, paper exit roller stop)                                                                                                                                            | ↓<br>Step 45:      | Copier mirror base scanning stop                                                                                                                              |

| ¥<br>Step 31:<br>│          | Transport motor (DTM) OFF<br>(Transport belt rotation)                                                                                                                                                         | ↓<br>(Reverse      |                                                                                                                                                               |

| ↓<br>Step 32:               | Reverse motor (DRM) forward rotation                                                                                                                                                                           | rotation)          |                                                                                                                                                               |

|                             | (Reverse roller, paper exit roller rotation)<br>The document is transported to the paper<br>feed section.                                                                                                      | ↓<br>Step 46:<br>↓ | Reverse solenoid (DRSOL) ON<br>(The flapper moves up.)                                                                                                        |

| Step 33:                    | Paper exit sensor (RDD) senses the rear<br>edge of the reverse document.<br>(RDD output LOW)                                                                                                                   | Step 47:           | Transport motor (DTM) forward rotation<br>(Transport motor rotation)<br>Reverse motor (DRM) forward rotation<br>(Rreverse roller, paper exit roller rotation) |

| Step 34:<br>↓               | Reverse motor (DRM) OFF<br>(Reverse roller, paper exit roller stop)                                                                                                                                            | ↓<br>Step 48:<br>│ | Reverse sensor (RDD) senses the lead edge<br>of the document.<br>(RDD output HIGH)                                                                            |

| Step 35:                    | Transport motor (DTM) OFF<br>(Transport belt stop)<br>Document stop                                                                                                                                            | ↓<br>Step 49:      | The lead edge of the document is moved counterclockwise by the flapper.                                                                                       |

| ↓<br>Step 36:<br>↓          | Reverse solenoid (DRSOL) OFF<br>(The flapper moves down.)                                                                                                                                                      | ↓<br>Step 50:      | Transport motor (DTM) OFF<br>(Transport belt stop)                                                                                                            |

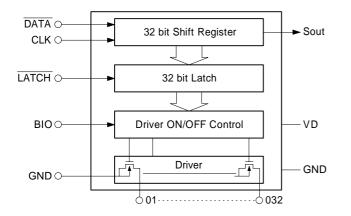

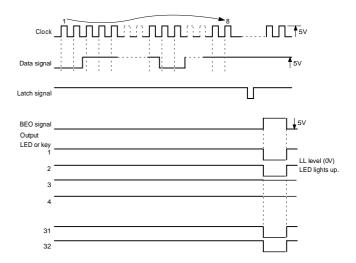

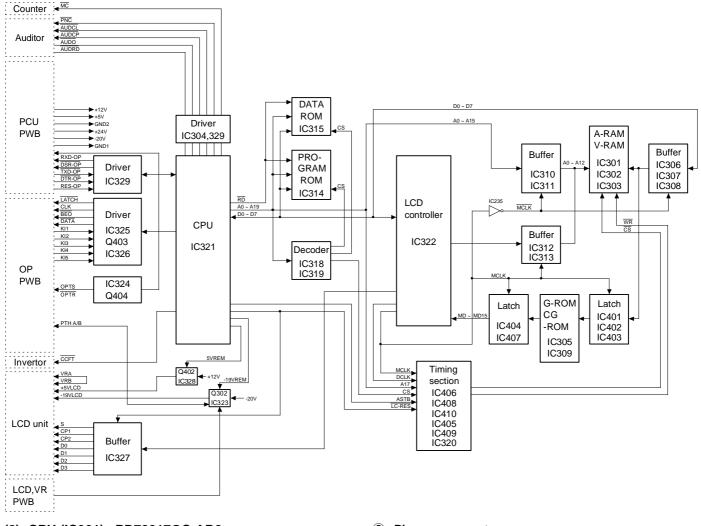

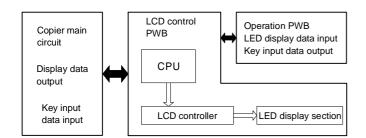

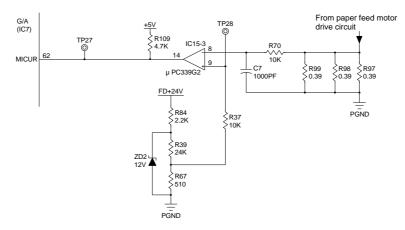

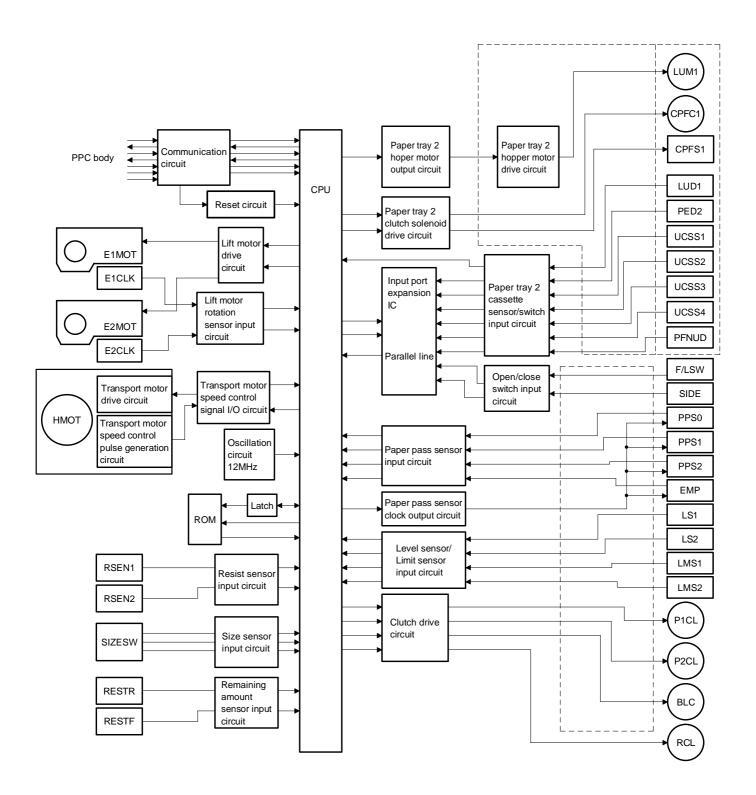

| Step 37:<br>★ D ↓<br>DSS ou |                                                                                                                                                                                                                | ↓<br>Step 51:      | Reverse motor (DRM) OFF<br>(Reverse roller, paper exit roller stop)                                                                                           |